Apple Phase bringt “King Fried Chips” in Jurassic Park Harte Philosophie

Bei Apples selbstentwickelter Chip-M1-Serie gibt es noch viele Rätsel.

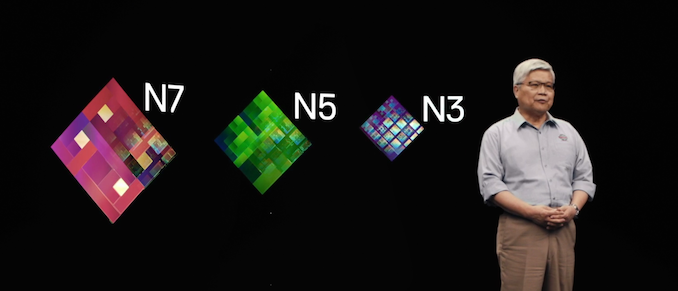

Gerade in letzter Zeit gab es viele Gerüchte über die Nachfolge der M1-Chips, M2 und M3, aber die meisten davon sind Informationen, die ins Auge fallen: Es gibt keine klaren Informationen zu Architektur, Leistung und Kern, aber mehr dazu TSMC: Upgrade von Prozessknoten.

▲ M1 ist noch nicht fertig, M2 und M3 kommen vielleicht bald. Bild von: Progamer

Die 4 nm, 3 nm und andere neue Prozesstechnologien von TSMC können größere Upgrade-Punkte darstellen. Auf diese Weise, in der M1-Serie, die bereits ein erstaunliches Energieverbrauchsverhältnis aufweist, steigen M2 und M3 nur an.

Aber wenn der Node-Prozess nach zwei Jahren auf 3 nm aufgerüstet wird?

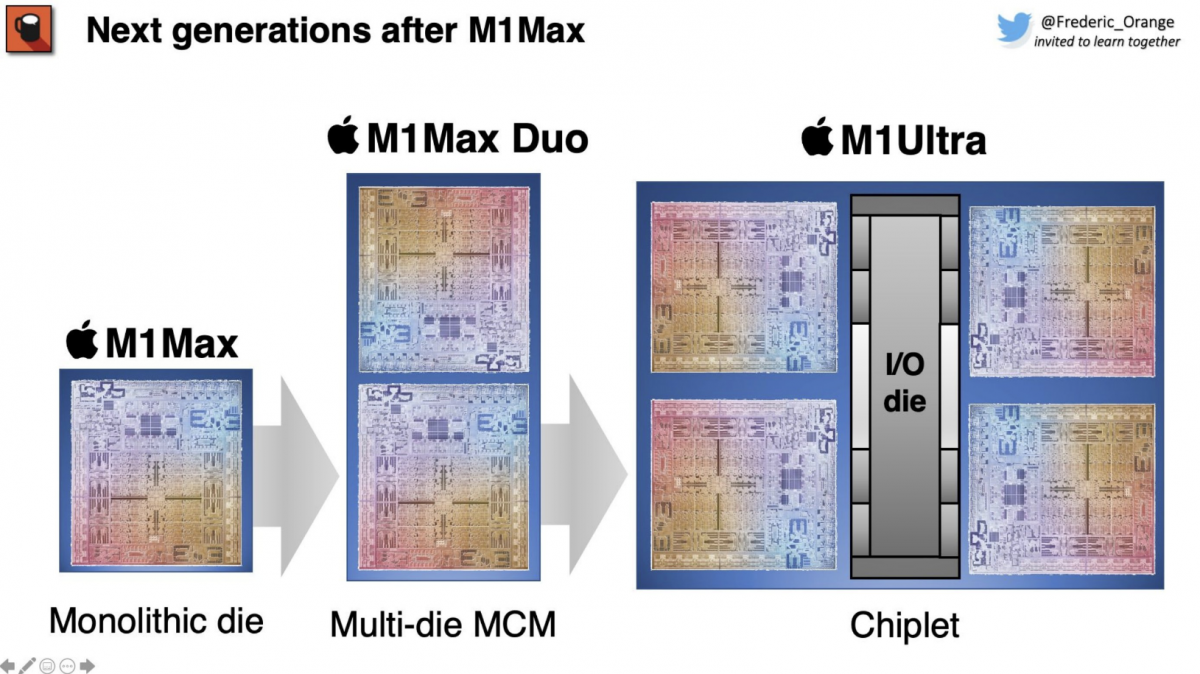

Es gibt ungefähr zwei, eine besteht darin, den Knotenprozess auf 1 nm zu trocknen, was sich drahtlos der physikalischen Grenze nähert, aber es ist schwieriger. Die andere besteht darin, die Vorteile von Knotenprozess-Upgrades zu umgehen und den Weg der "kleinen Chips" von Chiplet zu gehen.

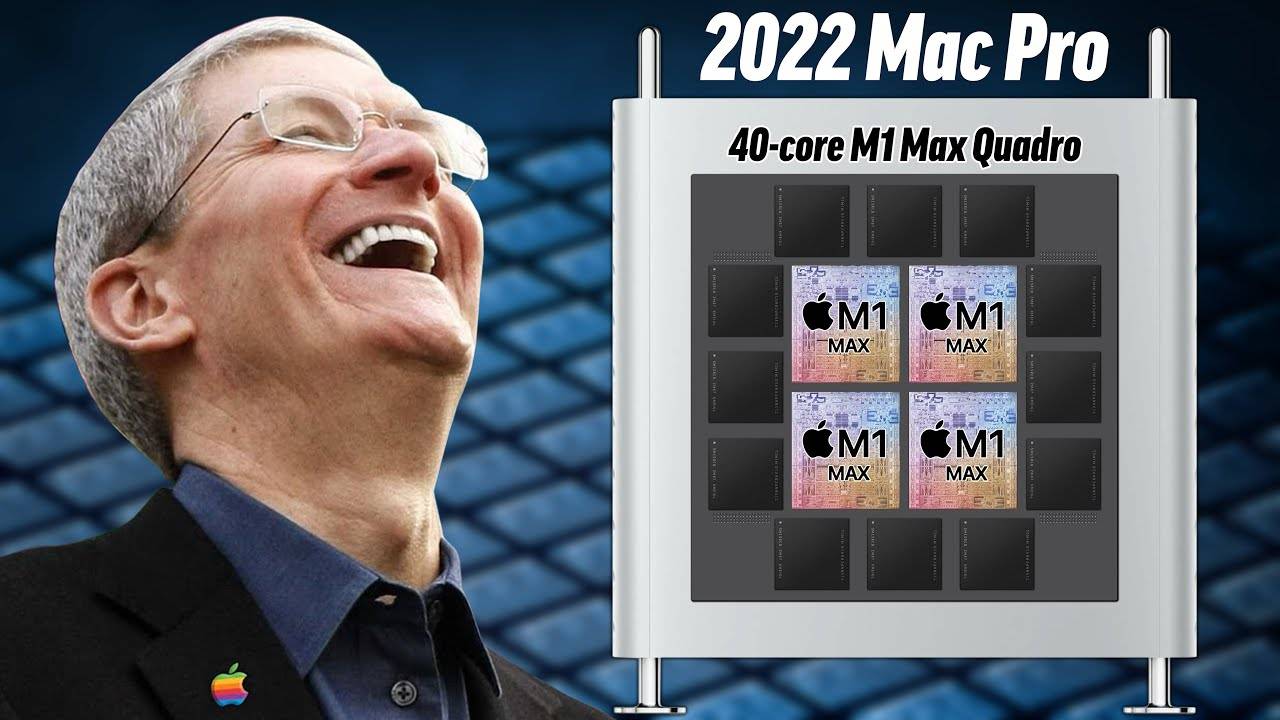

Ist ein M1 Max nicht genug? Installieren Sie dann zwei Mac Pro

Apple, das es immer nicht gemocht hat, der Lieferkette ausgeliefert zu sein, sucht möglicherweise nach einem praktikablen Weg und nutzt gleichzeitig die hohe Energieeffizienz von Knoten und ARM-Chips.

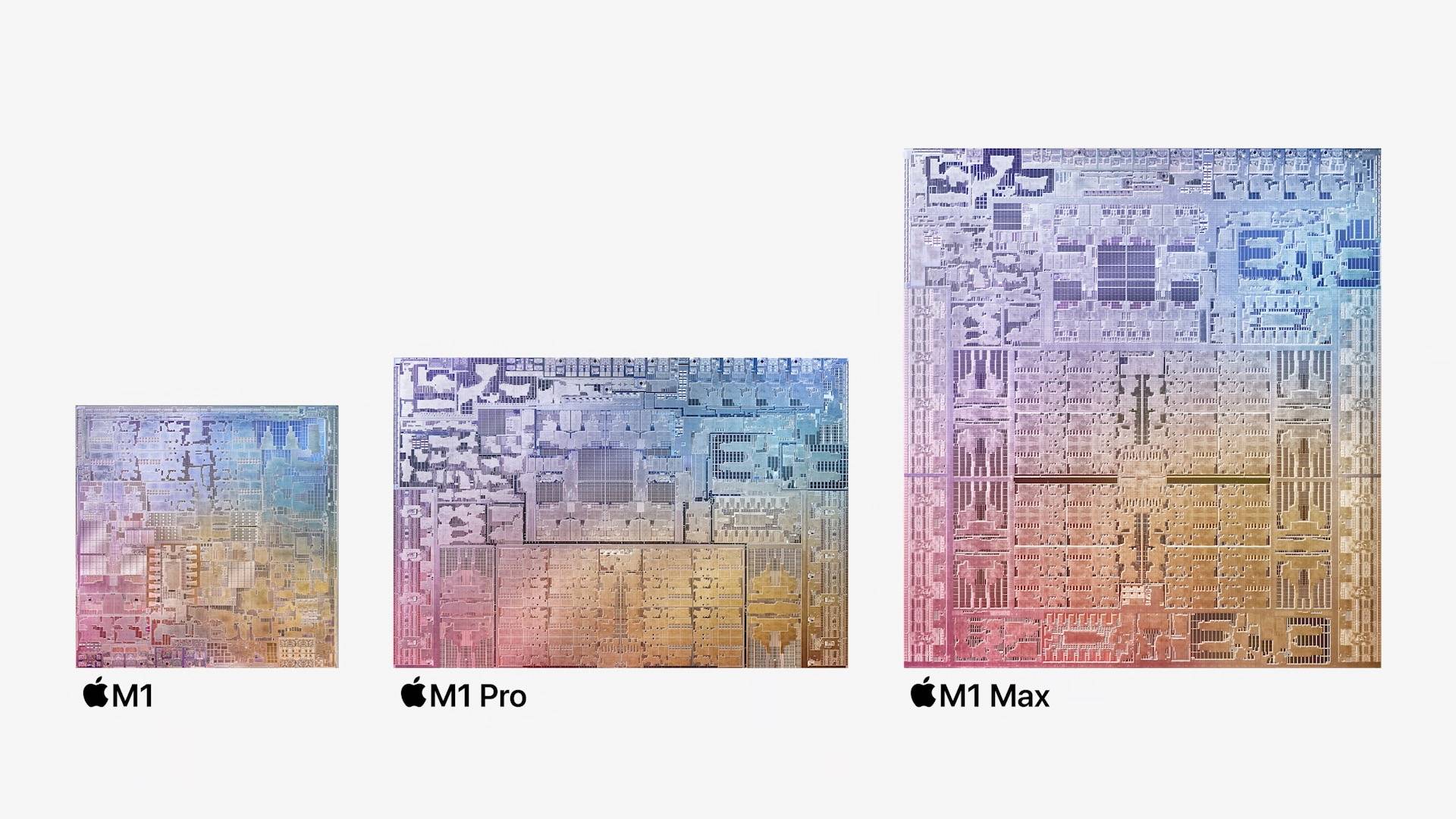

Von M1 bis hin zu den leistungsstärkeren M1 Pro und M1 Max haben sie fast die gleiche Architektur.Die Leistungsfreigabe von Single-Core ist relativ nah.Der größte Unterschied ist eigentlich die Anzahl der Kerne.

Sie können sogar einfach verstehen, dass ARM-basierte M-Chips auf die Anzahl der Heap-Kerne angewiesen sind, um eine höhere Leistungsgrenze zu erreichen.

- M1: CPU 4+4 Kerne, GPU 8 Kerne, 16 Milliarden Transistoren, 16 Kern neuronales Netzwerk;

- M1 Pro: CPU 2+8 Kerne, GPU 16 Kerne, 33,7 Milliarden Transistoren, 16 Kern neuronales Netzwerk;

- M1 Max: CPU 2+8 Kerne, GPU 32 Kerne, 57 Milliarden Transistoren, 16 Kern neuronales Netzwerk;

Aus einer anderen Perspektive beträgt die Chipfläche von M1 etwa 120 mm², während die von M1 Pro 245 mm² beträgt, bei M1 Max steigt sie direkt auf M1 Max 432 mm².

Für die gleiche Generation von M-Chips gilt: Je mehr Max, desto größer sind die Kernanzahl und die Chipfläche. Von hier aus ist es nicht schwer, Apples Namensregeln für M-Chips zu verstehen. Es ist leicht zu verstehen. Microsoft, Intel und Qualcomm sollte wirklich fleißig lernen.

Tim Millet, Apples Chiparchitekt und Vizepräsident, erläuterte zwar ausführlich im Upgrade-Podcast im November Apples hart arbeitende Reise bei der Entwicklung des M-Chips, aber für die nächste Entwicklung des M-Chips, und wie man Max anhand dessen ändert von Max hat kein Wort erwähnt.

▲ Apple Chiparchitekt und Vizepräsident Tim Millet (Tim Millet). Bild von: Apple

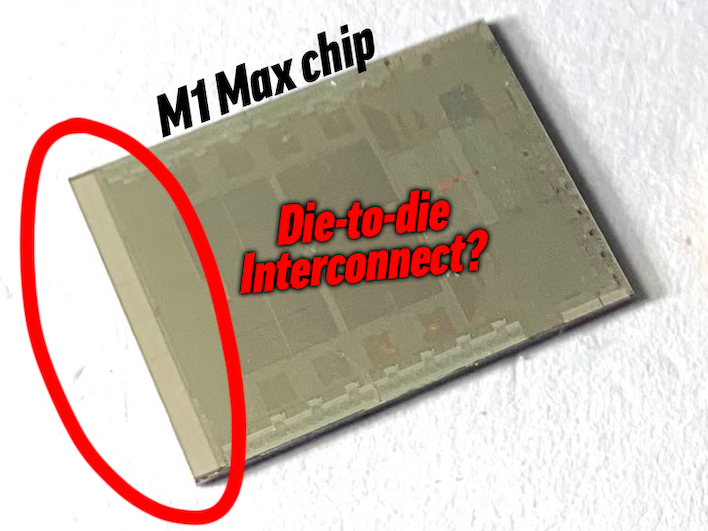

Nachdem das MacBook Pro 14/16 nacheinander auf den Markt gekommen ist, scheint es nach vielen privaten Heimwerker-Erkundungen, dass Apple auch das M1 Max mehr Max vorweggenommen hat.

Das heißt "Setzen Sie zwei M1 Max ein, und Sie können es sogar verdoppeln."

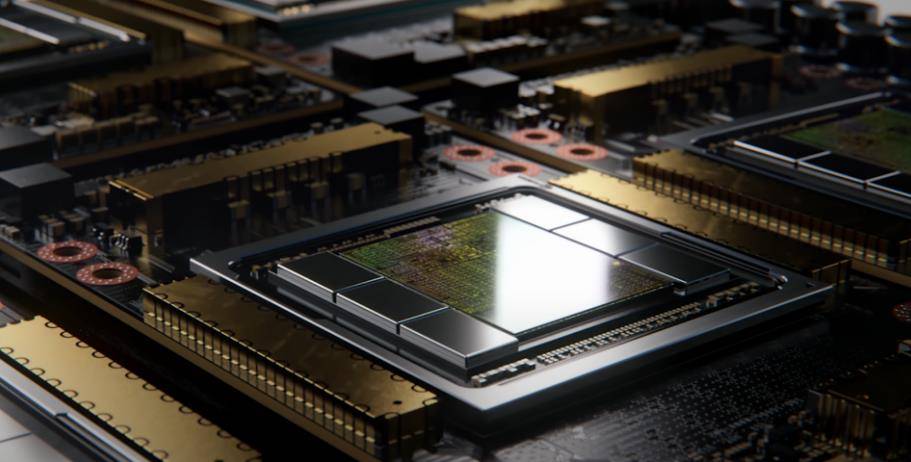

▲ M1 Max versteckter Bereich. Bild von: HothardWare

Diese Vermutung basiert eigentlich auf der Demontage und stellte fest, dass der M1 Max im Vergleich zum M1 Pro einen zusätzlichen "unbekannten Bereich" hat. Nach einigem Brainstorming wird vermutet, dass es sich um einen "Hochgeschwindigkeitsbus" handelt, der für die Verbindung von zwei oder mehr reserviert ist M1 max.

▲ Tim Cook: Intel, das ist für dich Bild von: Max Tech

Dies passt auch zu den Gerüchten, dass der neue iMac Pro und der Mac Pro mehrere M1 Max-Prozessoren verwenden werden. "Es ist, als würde man Lego spielen, Holz stapeln und den Meister wahllos schlagen."

Der Begriff "Holzhaufen" ist jedoch nicht sehr genau und "Puzzle" ist genauer. Auf diese Weise wird die Chipfläche des doppelten M1 Max ziemlich groß, und das vierfache ist beispiellos.

M1 Max Duo übertrifft Nvidias Top-GPU GA100. Die Chipfläche (826 mm²) ist fast sicher.

Betrachtet man die gesamte Halbleitergeschichte, kann ein so riesiger SoC definitiv als Chip auf "Tyrannosaurus"-Niveau gezählt werden, ganz zu schweigen davon, dass er auf einem 5-nm-Prozess basieren wird und die Kosten sehr wahrscheinlich jeden modernen Chip übersteigen werden.

Wenn Chips der M-Serie "Jurassic Park" betreten

Vom ursprünglichen Computer ENIAC mit einem Gewicht von 30 Tonnen und einer Fläche von 170 Quadratmetern bis hin zum aktuellen Desktop-PC entwickeln sich fast alle Geräte in Richtung Miniaturisierung und Integration.

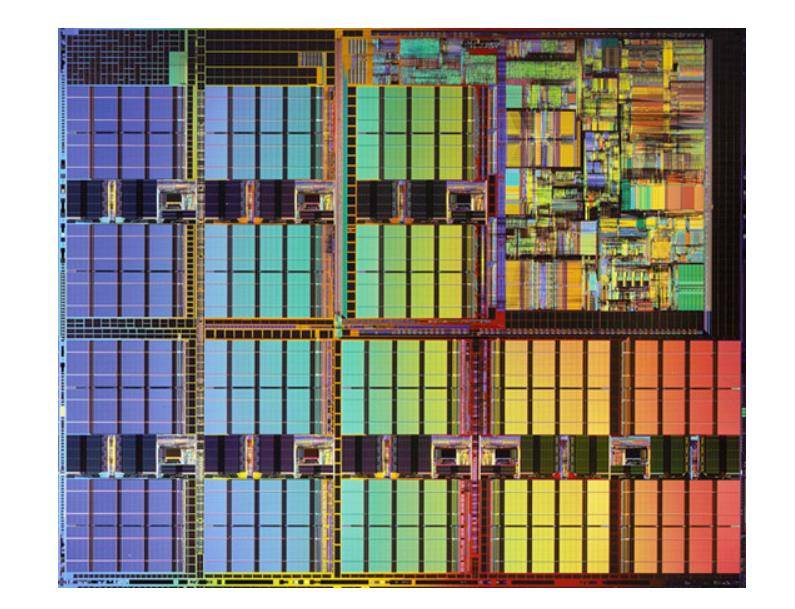

Gleiches gilt für Prozessoren in der Halbleiterwelt: Wenn der Prozessknoten noch µm beträgt, beträgt die Fläche von Intels erstem Pentium (Pentium) etwa 294 mm², basierend auf dem 0,8 µm-Prozess.

▲ Intel Pentium III Xeon.

In der x86-Prozessor-Ära hat Intel Pentium III Xeon eine Fläche von 385mm² und basiert auf einem 0,18μm-Prozess. Zu dieser Zeit kontrollierten jedoch viele Prozessorhersteller streng das Volumen und drückten die Kosten und führten relativ erschwingliche PCs ein, um sie der breiten Öffentlichkeit zu präsentieren.

In Zukunft, sei es die Popularität von 64-Bit oder der Sprung von Prozessknoten, wird die Größe des Prozessors meist unter 500 mm² kontrolliert.Unter der Prämisse der Kostenkontrolle und des effizienten Einsatzes von Wafern hat dies den Verbraucher fast gestoppt. Klasse Prozessor vor der "Dinosaurierisierung". "Entwicklung von.

Die Consumer-Halbleiterindustrie scheint allmählich vom Jura in eine neue Ära übergegangen zu sein.

▲ Auch Volksgötter machen Vorschläge für die Entwicklung von Apples M-Chip. Bild von: Twitter

Zu diesem Zeitpunkt scheint sich der mögliche Entwicklungsweg von Apples M-Chip in den "Jurassic" zurückgedreht zu haben, aber während die Größe des Prozessors vorangeschritten ist, ist die Dichte der Transistoren nicht gesunken.

Obwohl es sich so anhört, als ob es nicht schwierig sein sollte, zwei Chips zusammenzubauen, und es besteht keine Notwendigkeit, die Architektur und den Kern neu zu entwerfen. Aber in Wirklichkeit steigen die Kosten mit der Zunahme der Chipfläche (insbesondere dem verdoppelten Wachstum) und der Gewährleistung ausreichender Ausbeute und Produktionskapazität direkt.

Apples Chips der M-Serie sind immer noch Consumer-Produkte, vor einem Jahr hat man Intel abgeschafft, um einerseits die Produktstärke zu kontrollieren, andererseits die Kosten zu kontrollieren und den Gewinn zu maximieren. Die schwankenden Kosten eines großflächigen SoCs entsprechen eindeutig nicht den Erwartungen von Apple.

▲ Der höchste vereinheitlichte Speicher von M1 Max ist 64 GB, dann kommt M1 Max Duo direkt auf 128 GB?

Werden hingegen zwei oder mehr M1 Max zusammengespleißt, stellt das Design von Unified Memory (UMA) ebenfalls ein großes Problem dar. Planen Sie den Standort des Multicores neu, führen Sie größere Bandbreite und höhere Kapazität ein Erinnerung Es ist unvermeidlich.

Für die Öffentlichkeit kann es ein komplizierteres Chipdesign sein, und für den Privaten kann es die Kosten um ein Vielfaches erhöhen, was zwei große Stolpersteine für Apples M-Chip sein wird, um mehr Max zu werden.

Moores Gesetz ist Vergangenheit, der Moment ist jetzt

„Die Anzahl der Transistoren, die auf einem integrierten Schaltkreis untergebracht werden können, wird sich etwa alle zwei Jahre verdoppeln.“ So lautet das berühmte Mooresche Gesetz, und es heißt auch: „Alle 18 Monate verdoppelt sich die Leistung des Chips.“

▲ MacBook Pro 16. Bild von: dpreview

Die Leistung bezieht sich hier eigentlich auf die Anzahl der Transistoren.Im Vergleich zu M1 hat M1 Max eine 3,5-fache Leistungssteigerung, was zufällig den Unterschied in der Anzahl der Transistoren widerspiegelt.

Die Anzahl der Transistoren hat sich in der M1-Serie verdoppelt, was eine Zunahme der Chipfläche bedeutet. Aus historischer Sicht ist es eher vom technologischen Fortschritt abhängig, vom µm- bis zum nm-Niveau ist auch die Zahl der Transistoren von einer Million auf einhundert Millionen gesprungen.

Um das Jahr 2013 herum hat sich das Mooresche Gesetz jedoch verlangsamt: Von damals bis heute sind die Leistungsvorteile der Verbesserung von Prozessknoten rückläufig.

Durch fortschrittlichere technologische Prozesse kann zwar die Anzahl der Transistoren erhöht werden, es gehen aber auch Kosten- und Ertragsänderungen einher.

▲ TSMC wird voraussichtlich 2023 mit der Produktion des 3nm-Prozesses beginnen. Bild von: anandtech

Nach Angaben der International Business Strategy Corporation (IBS) wird die Entwicklung eines 3nm-Chips voraussichtlich 590 Millionen US-Dollar kosten, während 5nm nur 416 Millionen US-Dollar kostet, 7nm 217 Millionen US-Dollar und 28nm nur 40 Millionen US-Dollar kosten Dollar.

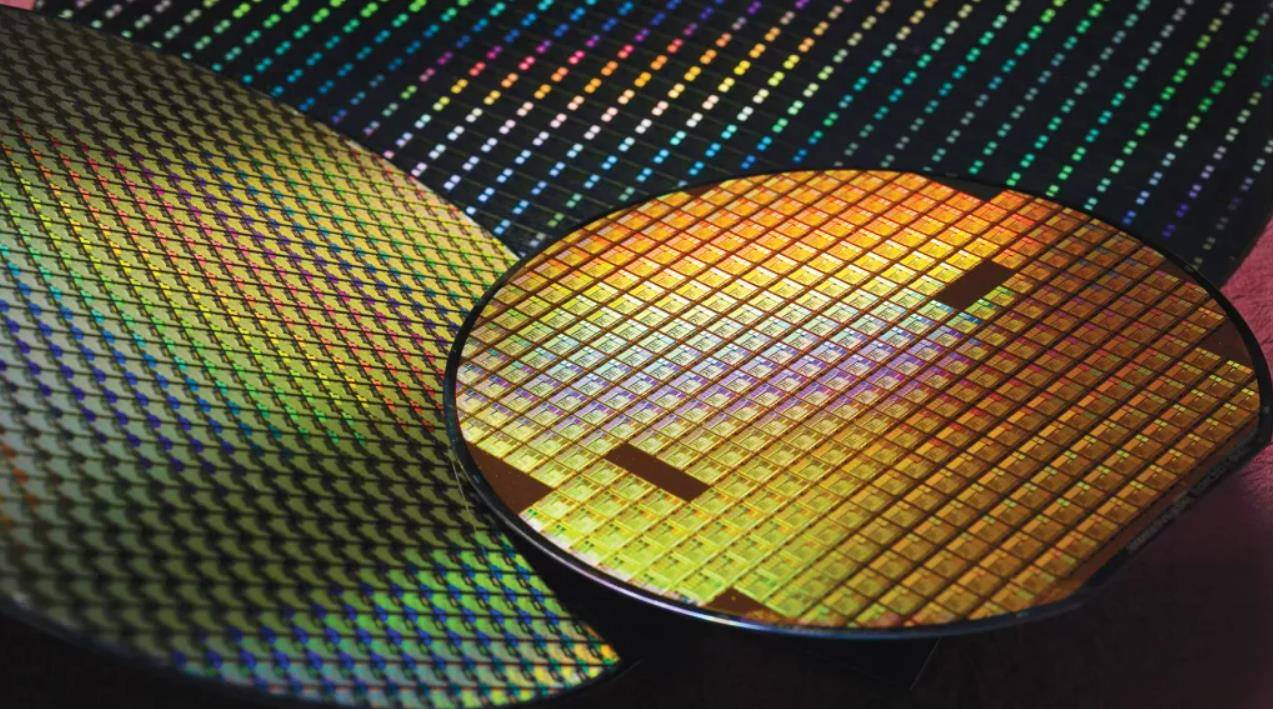

TSMC hat zuvor angekündigt, 20 Milliarden US-Dollar in den Bau einer 3nm-Waferfabrik zu investieren, auch für 3nm sind die Kosten von Samsung nicht niedriger als die von TSMC.

Bisher setzen nur TSMC und Samsung aktiv 3-nm-Wafer ein, andere Hersteller wollen, können sich das Geld aber nicht leisten.

Andererseits sinkt die Ausbeute an Chips mit zunehmender Fläche.Die Design-Pass-Rate von 700 mm² beträgt nur etwa 30 %.Wenn sie auf 150 mm² reduziert wird, steigt die Ausbeute auf 80 % an.

Egal wie man es betrachtet, der Weg zu Chip-Upgrades scheint versperrt zu sein.

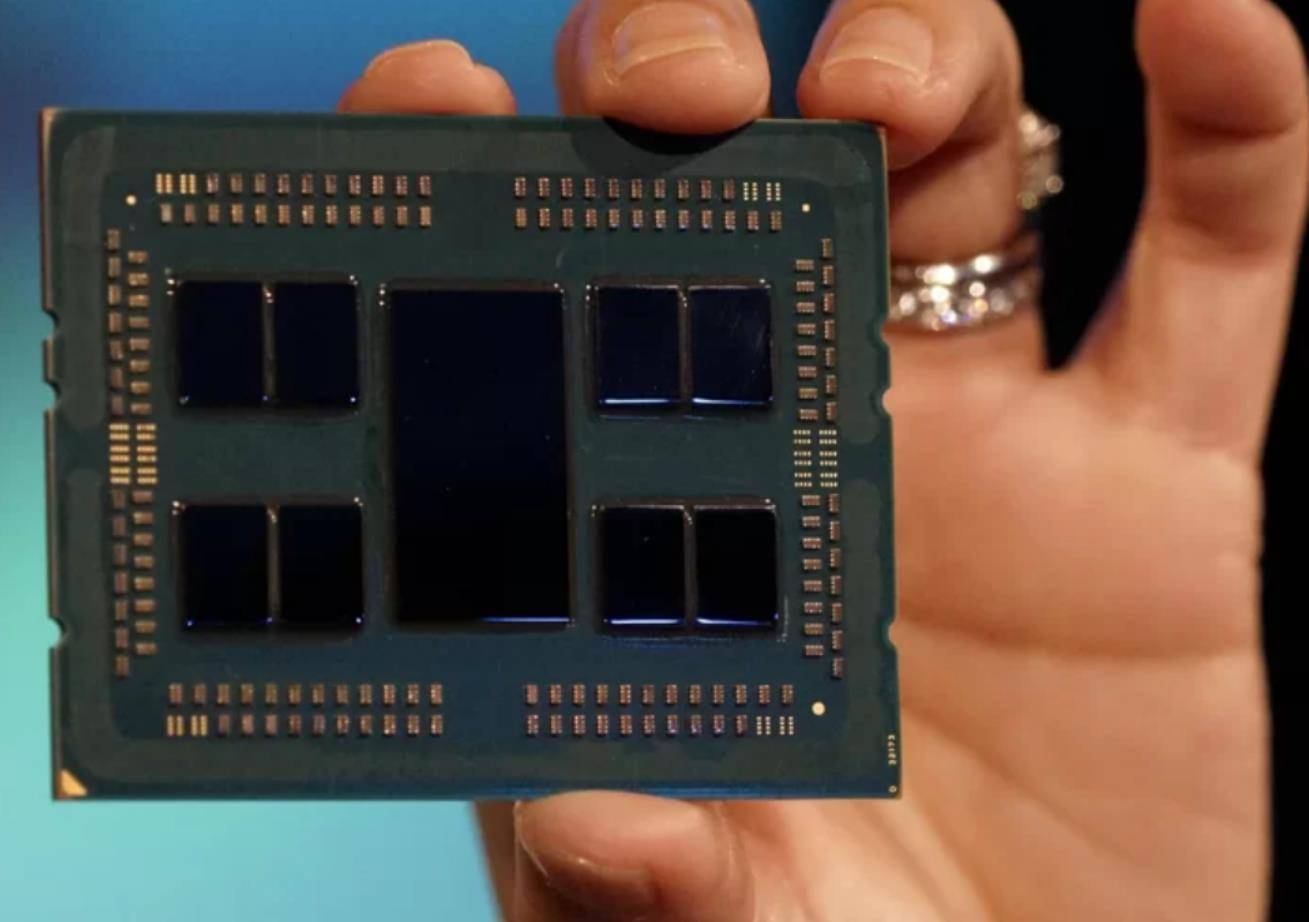

▲ AMD EPYC 2 (Rome) Prozessor basierend auf Zen 2. Bild von: AMD

Um die Chipgröße und -dichte weiter zu erhöhen, haben viele Menschen ihre Aufmerksamkeit von der Aufrüstung des Prozessknotens auf den Verpackungsprozess gerichtet, bei dem es sich um AMDs Chiplet (Small Chip)-Technologie handelt.

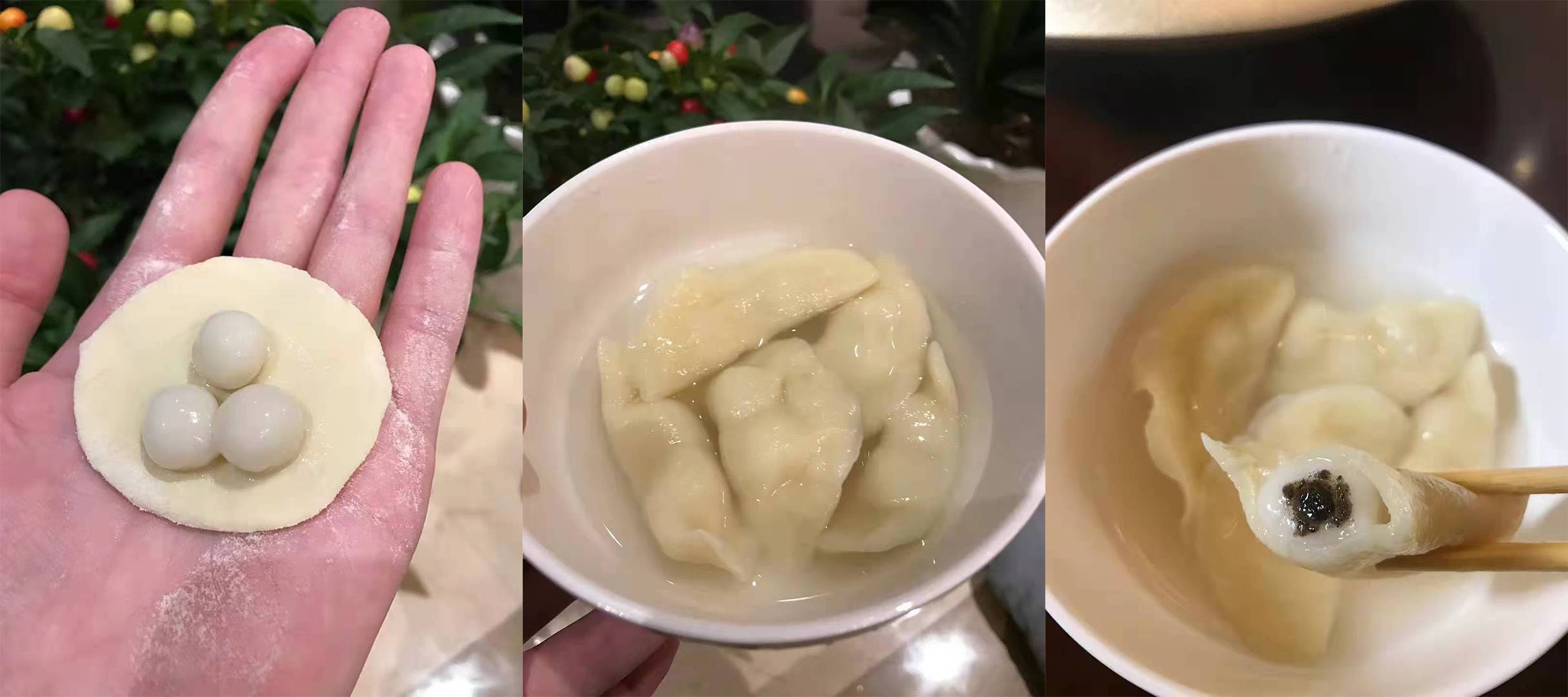

Einfach ausgedrückt ist Chiplet wie mit Klebreisbällchen gefüllte Teigtaschen, die kleine Chips mit unterschiedlichen Funktionen zusammen einkapseln, anstatt direkt aus der Waffel zu schneiden, und mit fortschrittlicher Verpackungstechnologie die Stagnation des Prozessknotens ausgleichen.

▲ Derzeit die anschaulichste Metapher für Chiplet (aber ich befürworte diese Art des Essens nicht).

In den letzten Jahren hat AMD auch die Chiplet-Technologie verwendet, um die Prozessordichte kontinuierlich zu erhöhen, um Intel entgegenzuwirken, und begann allmählich, den Markt zu erobern.

Für Chiplet, das in den letzten Jahren entstanden ist, hat The Linley Group, eine maßgebliche Beratungsorganisation in der Technologiebranche, direkt vorgeschlagen, dass Chiplet die Designkosten großer 7-nm-Chips um mehr als 25 % senken kann im Artikel „Why Big Chips Are Getting Klein". Während des Prozesses werden die Kosteneinsparungen noch höher sein.

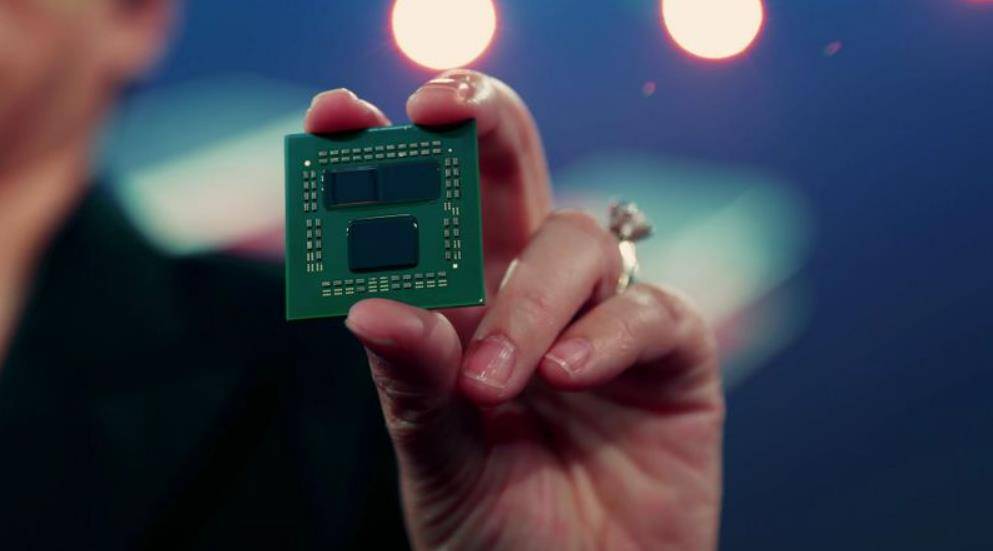

▲ AMD basiert auf der Ryzen 9 5900X CPU in einem 3D-Chiplet-Paket.

Und der von AMD angekündigte 3D-V-Cache bestätigt auch, dass Chiplet, das den alten Prozess und den fortschrittlichen Verpackungsprozess kombiniert, mit genügend Flexibilität eine höhere Knotenleistung erzielen und sogar Chips aus verschiedenen Prozessknoten mischen kann.

Neben Kostensenkung und Leistungssteigerung wird Chiplet auch Produkteinführungen beschleunigen, schließlich reicht es aus, alte Chips direkt mit Advanced Packaging-Prozessen zu verwenden und sogar das Layout von Advanced Process Nodes zu ignorieren.

Bei so vielen Vorteilen hat Chiplet auch entsprechende Nachteile: Das Stapeln von kleinen Chips 2D und 3D stellt sehr hohe Anforderungen an das Design des Thermomanagements, und die gesamte thermische Leistungsaufnahme im Gehäuse wird deutlich verbessert.

▲ Intel Serverchip basierend auf Chiplet. Bild von: nextplatorm

Auf jeden Fall wurde Chiplet von vielen Institutionen und Herstellern als wichtige Technologie für kontinuierliche Durchbrüche in der Chipleistung in der Post-Moore-Ära anerkannt.

▲ M1 im Mac mini und MacBook Air.

Zurückgehend auf den ursprünglichen, von Apple selbst entwickelten M-Chip, wird durch die ARM-Architektur und die Aufrüstung der Prozessknoten das Energieeffizienzverhältnis kontinuierlich verbessert, Ausbeute und Kosten werden ganz nebenbei kontrolliert. Ob es mehrere M1 Max zu einem komplexen Riesen-SoC zu einem Mac Pro auf Workstation-Ebene kombinieren wird, hat Apple aus heutiger Sicht genug Kapital und Kraft, um einen "prähistorischen Giganten"-Prozessor zu entwickeln und zu produzieren.

▲ Inoffizielles Rendering von iMac Pro 2022.

Chiplet muss meiner Meinung nach in den Zeichnungen des Apple-Chip-Teams erschienen sein.Anstatt sich dem zukünftigen ungewissen Prozess-Node-Upgrade zu stellen, ist es besser, aktiv nach Änderungen zu suchen und sich darauf zu verlassen, dass der aktuelle M-Chip und der A-Chip kombiniert werden, um sie abzuschließen ein tieferes SoC-Upgrade.

#Willkommen, um dem offiziellen WeChat-Account von Aifaner zu folgen: Aifaner (WeChat-ID: ifanr), weitere spannende Inhalte werden Ihnen so schnell wie möglich zur Verfügung gestellt.

Ai Faner | Ursprünglicher Link · Kommentare anzeigen · Sina Weibo