Wie unterscheiden sich RISC- und CISC-CPUs?

Wenn Sie ein Technik-Enthusiast sind, haben Sie vielleicht schon die Wörter Reduced Instruction Set Computer (RISC) und Complex Instruction Set Computer (CISC) gehört. Und wenn Sie sich mit Computern gut auskennen, wissen Sie vielleicht auch, dass sich diese Begriffe auf verschiedene Arten der Entwicklung eines Prozessors beziehen.

Der ARM-Prozessor in Ihrem Telefon hat beispielsweise eine RISC-Architektur. Im Gegensatz dazu hat der x86-Prozessor Ihres Computers ein CISC-Design.

Aber was ist der Unterschied zwischen RISC und CISC? Lassen Sie uns ein wenig tiefer eintauchen und es herausfinden.

Was ist ein Befehlssatz?

Immer wenn wir über verschiedene Designs der Zentraleinheit (CPU) sprechen, müssen wir unter anderem über den Befehlssatz sprechen.

Der Befehlssatz einer CPU ist der Satz von Operationen, die eine CPU nativ ausführen kann. Dies sind die Operationen, die in der CPU auf Hardwareebene kodiert sind. Dieser Satz kann je nach CPU-Design einige bis Tausende von Befehlen enthalten.

Mit anderen Worten, eine CPU kann keine Operation ausführen, die außerhalb ihres Befehlssatzes liegt, da sie nicht über die Hardware dafür verfügt.

Lassen Sie uns eine Analogie verwenden, um dies besser zu verstehen. Nehmen Sie das Beispiel einer Glühbirne. Der Hersteller einer Glühbirne hat die Glühbirne so konzipiert, dass sie Strom in Licht umwandelt. Und eine Glühbirne kann dies, weil die Hardware dies nativ unterstützt.

Im Wesentlichen kann eine Glühbirne nur Strom in Licht umwandeln und sonst nichts.

Ähnlich ist der Befehlssatz einer CPU der Satz von Operationen, den die Hardware der CPU ermöglicht. Zum Beispiel haben fast alle CPUs einen „Move“-Befehl in ihrem Befehlssatz. Die Anweisung „Move“ nimmt einige Daten aus einem Quellspeicherplatz und verschiebt sie in einen Zielspeicherplatz.

Immer wenn eine CPU Daten verschieben muss, weiß sie genau, wie es geht, da die Hardware darauf ausgelegt ist.

Kurz gesagt enthält ein Befehlssatz alle Operationen, die eine CPU auf Hardwareebene unterstützt.

Wie funktioniert eine CPU?

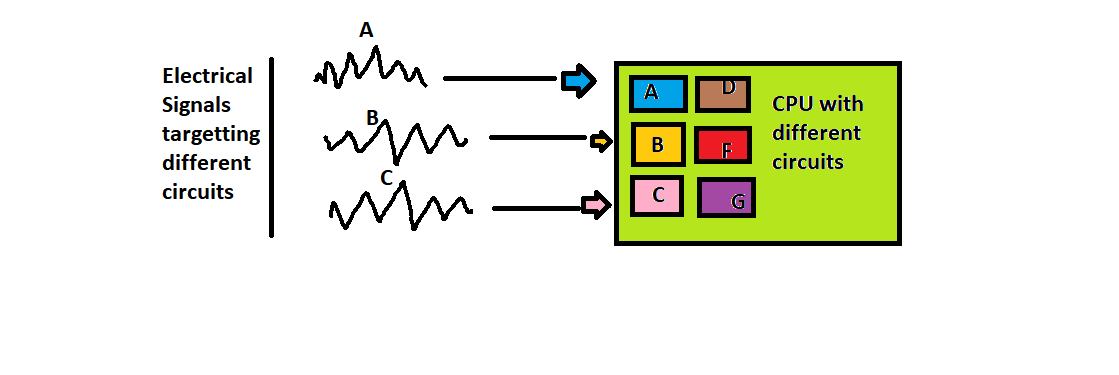

Eine CPU ist ein Labyrinth aus elektrischen Schaltkreisen. Diese elektrischen Schaltungen sind auf eine bestimmte Weise entworfen, um der CPU ihren nativen Befehlssatz zu geben. Es weiß also nur, wie die Operationen in einem Befehlssatz auszuführen sind, da es über die dafür erforderliche Schaltung verfügt.

Um die CPU zu veranlassen, eine bestimmte Operation auszuführen, wird die dieser Operation entsprechende Schaltung durch ein elektrisches Signal getriggert. Und sobald eine Schaltung getriggert ist, führt die CPU die dieser Schaltung zugeordnete Routine aus.

Damit die CPU komplexe Operationen wie das Senden eines Tweets ausführt, feuern Softwareprogramme jede Sekunde Millionen elektrischer Signale ab, die jeweils auf eine bestimmte Anweisung aus dem Befehlssatz der CPU abzielen.

Hier setzt das Konzept von RIS und CIS an.

Was ist RISC?

Wie der Name schon sagt, verfügt eine RISC-basierte CPU über einen vereinfachten Satz von Operationen. Diese vereinfachten Anweisungen erreichen einfache Ziele und benötigen nur einen Zyklus.

Und da RISC einfache Befehle hat, braucht die CPU keine komplexen Schaltungen, um diese Befehle auszuführen. Dies ist auch der Grund, warum RISC-Designs hardwaremäßig billiger zu implementieren sind.

Um eine RISC-CPU genauer zu verstehen, schauen wir uns die Designprinzipien von RISC-basierten CPUs an.

Erstens vervollständigen RISC-CPUs jeden Befehl in einem einzigen Zyklus.

Zweitens führen RISC-CPUs nur Operationen an Daten durch, die in Registern gespeichert sind. Dies liegt daran, dass einer der Hauptengpässe für die Fähigkeit einer CPU, Aufgaben zu erfüllen, die große Diskrepanz zwischen CPU-Geschwindigkeit und Hauptspeichergeschwindigkeit ist. Der Hauptspeicher ist im Vergleich zu einer CPU super langsam.

Wenn also eine CPU im Hauptspeicher gespeicherte Daten verwenden muss, führt dies zu einem Engpass für die Einheit und der Prozess würde langsam sein. Bei einem RISC-Design werden die Daten geladen und in den Registern der CPU gespeichert, da die Register viel näher an der CPU-Geschwindigkeit liegen als der Hauptspeicher.

Drittens sind RISC-Befehle einfach genug, dass es keine Schicht interpretierenden Mikrocodes gibt, um die Befehle in einfachere Formen zu übersetzen.

Und schließlich unterstützen RISC-Designs das Pipelining, um Teile mehrerer Anweisungen gleichzeitig auszuführen. Da CPUs im RISC-Design höhere Taktraten aufweisen, sind sie außergewöhnlich schnell. Pipelining ist eine Möglichkeit, diese Geschwindigkeit zu nutzen und Teile mehrerer Anweisungen für zusätzliche Effizienz auszuführen.

Kurz gesagt, RISC-CPUs haben einfache Befehle, höhere Taktgeschwindigkeiten, eine effiziente Pipeline-Struktur, Lade-Speicher-Operationen in den Registern und können Befehle in einem Zyklus ausführen.

Was ist CISC?

Der CISC ist in fast allen Schlüsselbereichen das Gegenteil von RISC. Fast alle Desktop-Chips haben ein CISC-Design.

Erstens sind CISC-Entwurfsanweisungen komplex und erfordern daher eine Mikrocodeschicht, um sie in Simplex-Anweisungen zu übersetzen.

Zweitens können CISC-Befehle mehrere CPU-Zyklen zur Ausführung benötigen.

Drittens ist Pipelining in CISC nicht so effizient und aufgrund der komplexen Natur der CISC-Befehle noch schwieriger zu implementieren.

Kurz gesagt, CPUs mit CISC-Architektur können viele Operationen in einem komplexen Befehl ausführen. Der Befehl benötigt jedoch mehrere Zyklen, ist beim Pipelining schwieriger zu verwenden und erfordert eine Menge Schaltungen auf der CPU.

RISC vs. CISC: Hauptunterschiede

Der Hauptunterschied zwischen RISC und CISC ist die Art der Anweisungen, die sie ausführen.

RISC-Befehle sind einfach, führen nur eine Operation aus und eine CPU kann sie in einem Zyklus ausführen.

CISC-Anweisungen hingegen packen eine Reihe von Operationen ein. Die CPU kann sie also nicht in einem Zyklus ausführen.

Anweisungen sind auch der Grund, warum RISC-CPUs Pipelining von Anfang an unterstützen und CISC-CPUs es damit schwerer haben. Bei RISC sind die Anweisungen so einfach, dass sie in Teilen ausgeführt werden können. Dies ist mit CISC aufgrund der Komplexität der Anweisungen schwieriger.

Als nächstes können CISC-Befehle im Gegensatz zu RISC direkt vom RAM aus arbeiten. Es besteht also keine Notwendigkeit, separate Lade-/Speicheroperationen im CISC-Design durchzuführen.

Schließlich sind die Hardwareanforderungen für ein CISC-Design höher als die für ein RISC-Design, da CISC erfordert, dass komplexe Befehle in die CPU-Hardware eingebaut werden. Was CISC mit Hardware leistet, will RISC mit der Software erreichen.

Aus diesem Grund haben Programme, die auf eine CISC-Architektur abzielen, weniger Codezeilen, da Befehle selbst viele Operationen verarbeiten.

Sowohl RISC als auch CISC haben Vor- und Nachteile

Kein moderner Prozessor basiert vollständig auf RISC oder CISC. Moderne Prozessoren integrieren die Designphilosophien beider Architekturen, um das Beste aus beiden Welten zu erreichen. Die von AMD verwendete x86-Architektur ist beispielsweise hauptsächlich CISC, verfügt jedoch über einen Mikrocode, um komplexe Anweisungen in einfache RISC-ähnliche reduzierte Anweisungen umzuwandeln.

Im Gegensatz zu den Prozessoren des letzten Jahrhunderts haben sich moderne CPUs also über eine einfache RISC- oder CISC-Klassifizierung hinaus entwickelt.